Frequency detector circuit

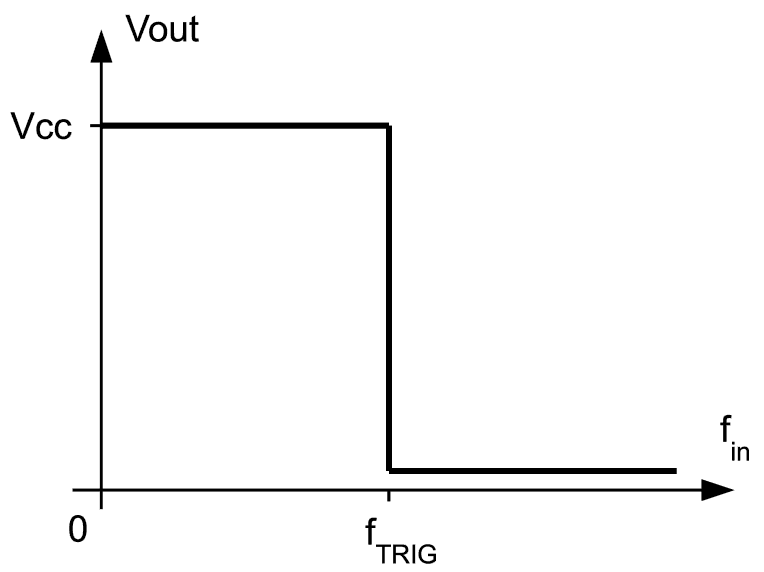

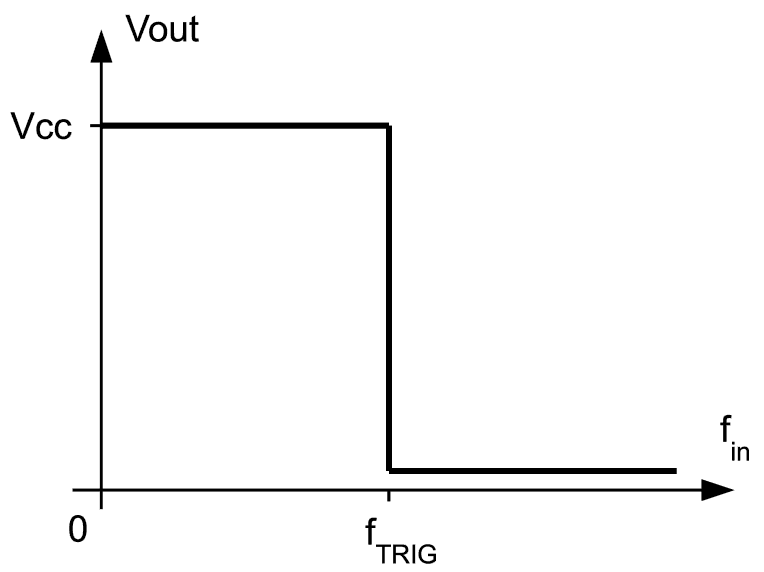

If in a particular application one is not interested in measuring and displaying the exact analog value of input signal frequency, but only needs to know whether the frequency is below or above a certain fixed value, all one has to do is to connect the output of the basic frequency metering circuit to an input of a voltage comparator. If comparator with wide hysteresis is acceptable, than the third gate of CD40106 IC can be used for that purpose.

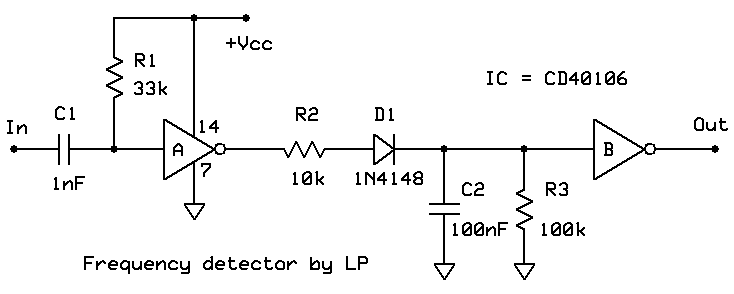

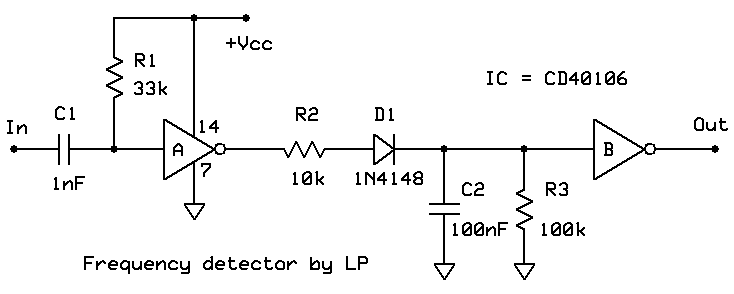

But there is an even simpler circuit able to react to a precisely defined frequency, consisting of not three but only two logic gates:

Instead of discharging C2, in this case trigger pulses charge it to voltage higher than 0V via D1 and a voltage divider consisting of R2 and R3. If there are no pulses, C2 remains discharged through R3, causing inverter B to keep its output at +Vcc. If pulses are very frequent, C2 voltage approaches Vcc*(R3/(R2+R3)), which is only a bit less than +Vcc. As soon as C2 voltage gets above 2/3Vcc, gate B changes its output state to 0V. This information can then be utilised further as desired. In case of the rain detector circuit, this turns on heating resistors and the noticeable increase in sensor overall current consumption is then used as an indication or rain. As has already been explained, the rise of the frequency is due to the decreasing resistance between the wetted interleaved rain sensing surface connections.

There is an important but not so obvious oddity of this circuit to note and remember. Some readers may find R2 unnecessary as it appears that a sole D1 is adequate to charge C2. But please remember that what we aim at is discerning pulses with frequency lower than a fixed threshold value from those with the frequency higher than that. Observe C1R1 high-pass filtering at the input of gate A, the purpose of which is to force gate A to generate positive pulses of short duration, which are then used to charge C2 as described. Since these pulses are very narrow, C2 gets charge in rather small constant amounts; only if pulses arrive frequently enough, will its voltage be able to rise above 2/3Vcc threshold - otherwise C2 gets discharged via R3 between each two successive pulses and as a result its voltage stays close to 0V. Voltage divider R2/R3 ratio of 1:10 seems to be a good rule of thumb with respect to achieving clean and relatively narrow transitional range in frequency domain (i.e. below and above the chosen threshold frequency). The exact threshold frequency depends predominantly on C2*R3 time constant. High-pass filter constant C1*R1 has to be much smaller than C2*R3, and also notably smaller than C2*R2. Due to hysteretic nature of gate B Schmidt-type input, once activated it needs the signal frequency to drop much below the “start” threshold for its output to turn back to inactive logic state. For example, if frequency detector is set to become active above 10kHz, it will deactivate only after input frequency drops below approximately 5kHz. We shall dive no deeper into the murky analysis in this article.

In the rain detector circuit described elsewhere at this web site there is no real necessity to spare every single logic gate as there are several of them left unused anyway. But in certain more elaborate circuits, logic gates being as inexpensive and ubiquitous as they are, usually are too useful to be wasted around - sometimes there is simply no place left on a PCB to insert an additional IC, while some other times a gate or two spared can be cunningly used to enrich the device with additional functionality (think LED blinker, BEEP generator etc).